Bien qu’Intel ait récemment publié les processeurs Core Core (S) Lake de 10e génération (Comet Lake-S), des rumeurs circulent déjà sur le Web non seulement au sujet de leurs successeurs au Rocket Lake-S (11e génération), mais même à propos de puces de 12e génération. Alder Lake-S. En particulier, il n’y a pas si longtemps, un arrangement inhabituel de ces derniers a été signalé, impliquant une combinaison de «grands» et de «petits» noyaux. Et maintenant, ces rumeurs sont partiellement confirmées.

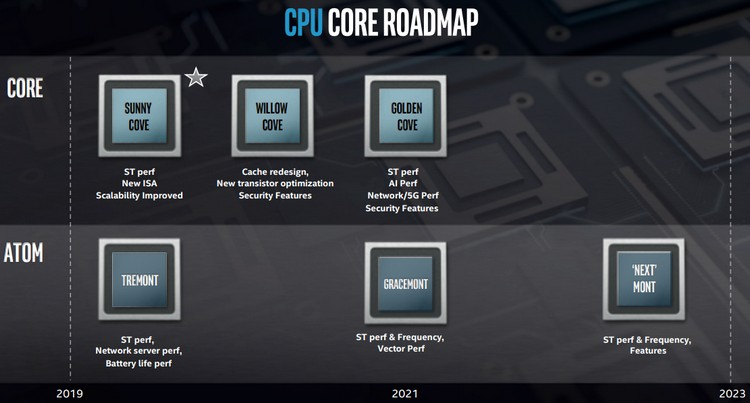

Selon des fuites d’informations antérieures, les processeurs Alder Lake-S contiendront jusqu’à seize cœurs, cependant, divisés en deux grappes. L’un d’eux combinera huit « grands » noyaux, apparemment avec l’architecture de Willow Cove ou de son successeur. Dans l’autre – les «petits» noyaux, très probablement avec l’architecture éconergétique de Tremont ou, encore une fois, avec son successeur. En basculant entre les clusters en fonction des tâches, les processeurs Alder Lake-S seront en mesure de fournir non seulement des performances élevées, mais également une meilleure efficacité énergétique.

De nouvelles indications sur la structure hybride des processeurs Alder Lake-S ont été trouvées dans le code de la dernière version du paquetage du compilateur GCC 11 sous GNU (GNU Compiler Collection 11). Il est rapporté que ces compilateurs ont été pris en charge à la fois par les processeurs de bureau Alder Lake-S et les générations de serveurs Xeon de Sapphire Rapids, qui devraient remplacer Ice Lake-SP.

Le GCC mis à jour prend en charge les nouvelles instructions qui apparaîtront dans les futurs processeurs. En même temps, comme l’a noté la ressource Phoronix, bien que, d’une part, les ordinateurs de bureau Alder Lake prennent en charge plusieurs nouveaux jeux d’instructions, d’autre part, ils manquent de quelques instructions prises en charge par les processeurs actuels. L’exemple le plus frappant est l’absence totale de prise en charge des instructions de l’ensemble AVX-512.

C’est précisément ce qui pointe vers l’architecture hybride. Apparemment, la prise en charge de l’AVX-512 dans les processeurs hybrides n’est pas possible à ce stade, en raison des particularités du planificateur du système d’exploitation qui les utilise. Bien que ces ensembles de commandes vectorielles soient garantis pour être pris en charge à la fois dans Sunny Cove et Willow Cove, ils ne sont pas implémentés dans les « petits » noyaux de la classe Tremont. Pour cette raison, les processeurs où les deux types de cœurs sont combinés ne reçoivent pas de support de l’AVX-512. Un exemple frappant ici peut être le processeur hybride Lakefield, combinant le « grand » cœur Sunny Cove avec le « petit » Tremont, dans lequel l’AVX-512 n’est pas pris en charge. De cela, nous pouvons conclure que dans le lac Alder, il y aura également des noyaux coexistants avec différentes architectures: à la fois à part entière et dépouillés.

Selon des données préliminaires, les processeurs Alder Lake-S arriveront sur le marché au début de 2022 et seront utilisés dans la nouvelle plate-forme de bureau LGA 1700, qui prendra en charge PCIe 4.0 et DDR5 SDRAM. Pour leur production, un procédé de fabrication de 10 nm de troisième génération sera utilisé.

Si vous remarquez une erreur, sélectionnez-la avec la souris et appuyez sur CTRL + ENTRÉE.